來源:壹芯微 發布日期

2019-09-17 瀏覽:-

來源:壹芯微 發布日期

2019-09-17 瀏覽:-cmos應用

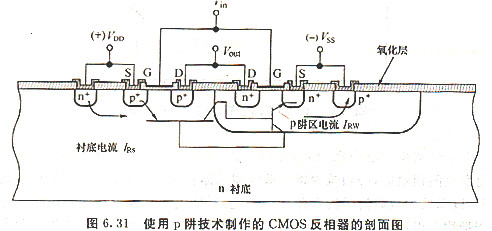

在CMOS應用中能同時將p溝道mos管與n溝道MOSFET制作在同一片芯片上.需要額外的摻雜及擴散步驟,以便在襯底中成“阱”或“盆(tub)”.阱中的摻雜種類與周圍襯底不同.阱的典型種類有p阱、n阱以及雙阱.阱技術的詳細內容將于第14章中討論.圖6. 31為使用p阱技術制作的CMOS反相器的剖面圖.在此圖中,p溝道與n溝道MoSFET分別制作于n型硅襯底以及p阱之中.

cmos電路

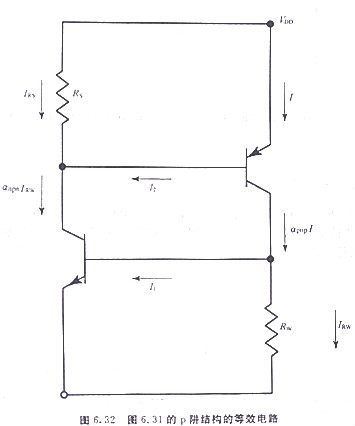

CMOS電路的阱結構最主要的問題在于閂鎖現象,閂鎖是由阱結構中寄生的pn—p-n二極管作用所造成的,如圖6.3】所示,寄生的p—n-I,一n二極管是由一橫向的p-n-p及一縱向的n-p-n雙極型晶體管所組成的.p溝道MOSFFT的源極、n襯底及p阱分別為橫向p-n-p雙極型晶體管的發射極、基極及集電極;n溝道MOSFET的源極、p阱及n襯底分別為縱向n-p-n雙極型晶體管的發射極、基極及集極其寄生部分的等效電路如圖6.32所示.凡及Rw分別為襯底及阱中的串聯電阻.每一晶體管的基極是由另一晶體管的集電極所MOS管驅動,并形成一正反饋回路,其架構就如第5章中所討論的可控硅器件( thyristor).閂鎖發生于兩個雙極型晶體管的共射電流增益乘積大于l時.當發生閂鎖時'一大電流將由電源供應處(Vpo)流向接地端,導致一般正常電路工作中斷,甚至會由于高電流散熱的問題.而損壞芯片本身.

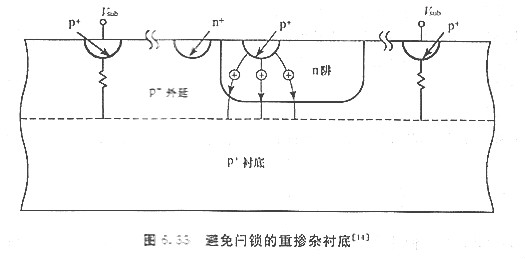

為避免發生閂鎖效應,必須減少寄生雙極型晶體管的電流增益,一種方法是使用金摻雜或中子輻射,以降低少數載流子的壽命,但此方法不易控制且也會導致漏電流的增加.深阱結構或高能量注入以形成倒退阱( retrograde well),可以提升基極雜質濃度,因而降低縱向雙極型晶體管的電流增益.在倒退阱結構中,阱摻雜濃度的峰值位于遠離表面的襯底中.另一種減少閂鎖效應的方法,是將器件制作于高摻雜襯底上的低摻雜外延層中,如圖6. 33所示.高摻雜襯底提供一個收集電流的高傳導路徑,這些電流隨后會由表面接點流出.

閂鎖亦可通過溝槽隔離(trench isolation.或譯溝渠絕緣)結構來加以避開,制作溝槽隔離的工藝將于第14章中討論.因為n溝道與p溝道MOSFET被溝槽所隔開,所以此種方法可以消除閂鎖.

壹芯微科技針對二三極管,MOS管作出了良好的性能測試,應用各大領域,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號