來源:壹芯微 發布日期

2022-10-09 瀏覽:-

來源:壹芯微 發布日期

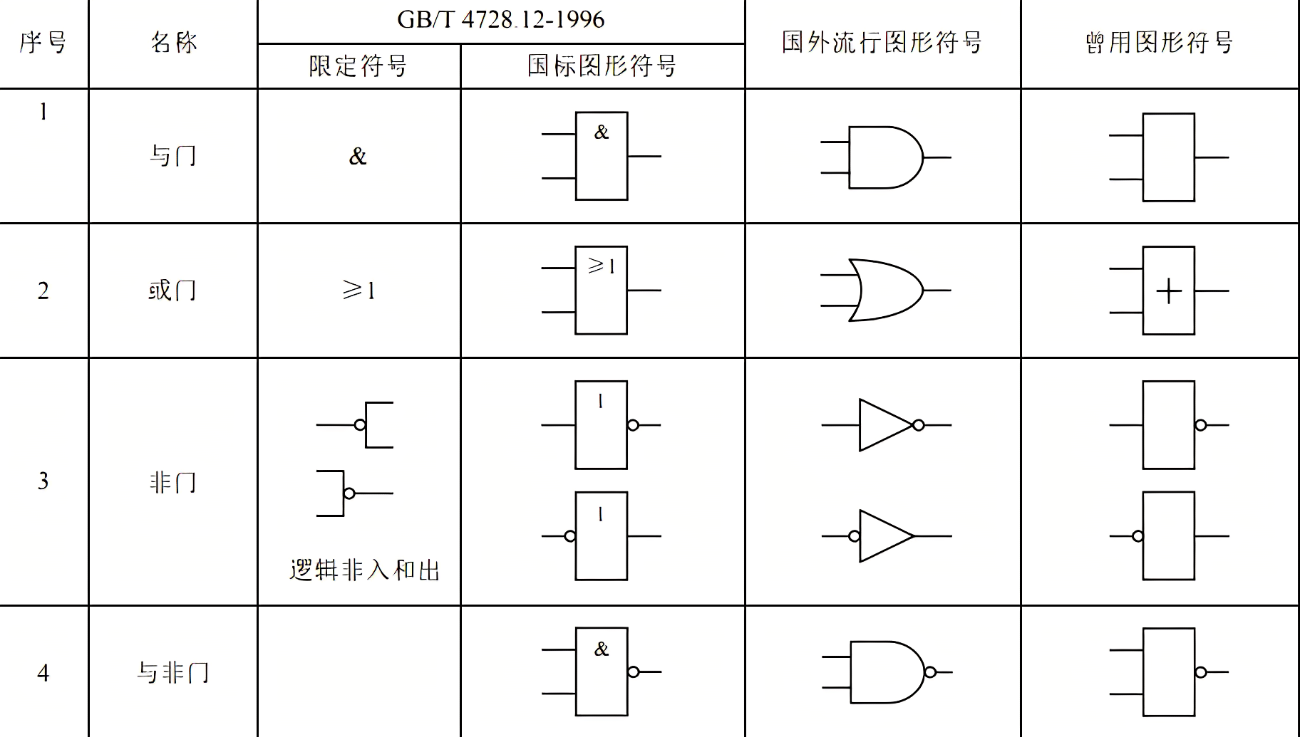

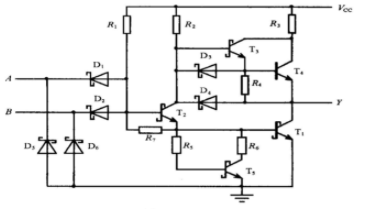

2022-10-09 瀏覽:-邏輯門電路指實現基本和常用邏輯運算的電子電路,也是集成電路上的基本組件。簡單的邏輯門可由晶體管組成,晶體管的組合可以使代表兩種信號的高低電平在通過它們之后產生高電平或者低電平的信號。接下來,為大家詳細說下邏輯門電路原理和邏輯門電路的主要技術參數。

一、邏輯門電路原理

首先考慮兩種極限情況:當vI處于邏輯0時,相應的電壓近似為0V;而當vI處于邏輯1時,相應的電壓近似為VDD。假設在兩種情況下N溝道管TN為工作管P溝道管TP為負載管。但是,由于電路是互補對稱的,這種假設可以是任意的,相反的情況亦將導致相同的結果。左圖分析了當vI=VDD時的工作情況。在TN的輸出特性iD—vDS(vGSN=VDD)(注意vDSN=vO)上,疊加一條負載線,它是負載管TP在vSGP=0V時的輸出特性iD-vSD。由于vSGP曲線幾乎是一條與橫軸重合的水平線。兩條曲線的交點即工作點。顯然,這時的輸出電壓vOL≈0V(典型值<10mV,而通過兩管的電流接近于零。這就是說,電路的功耗很小(微瓦量級)左圖分析了另一種極限情況,此時對應于vI=0V。此時工作管TN在vGSN=0的情況下運用,其輸出特性iD-vDS幾乎與橫軸重合,負載曲線是負載管TP在vsGP=VDD時的輸出特性iD-vDS。由圖可知,工作點決定了VO=VOH≈VDD;通過兩器件的電流接近零值。可見上述兩種極限情況下的功耗都很低。由此可知,基本CMOS反相器近似于一理想的邏輯單元,其輸出電壓接近于零或+VDD,而功耗幾乎為零。

二、邏輯門電路的主要技術參數

1、TTL電路的電源均采用+5V,使用時,不能將電源與地顛倒接錯,也不能接高于5.5V的電源。否則會損壞器件。

2、電路的輸入端不能直接與高于+5.5V或低于-0.5V的低內阻電源連接,因為低內阻電源供給較大電流而燒壞器件。

3、輸出端不允許與電源或地短接,必須通過電阻與電源連接,以提高輸出電平。

4、插入或拔出集成電路時,務必切斷電源,否則會因電源沖擊而造成永久損壞。

5、多余輸入端不允許懸空。接地電阻的阻值要求R≤=500。

壹芯微科技專注于“二,三極管、MOS(場效應管)、橋堆”研發、生產與銷售,20年行業經驗,擁有先進全自動化雙軌封裝生產線、高速檢測設備等,研發技術、芯片源自臺灣,專業生產流程管理及工程團隊,保障所生產每一批物料質量穩定和更長久的使用壽命,實現高度自動化生產,大幅降低人工成本,促進更好的性價比優勢!選擇壹芯微,還可為客戶提供參數選型替代,送樣測試,技術支持,售后服務等,如需了解更多詳情或最新報價,歡迎咨詢官網在線客服!

手機號/微信:13534146615

QQ:2881579535

工廠地址:安徽省六安市金寨產業園區

深圳辦事處地址:深圳市福田區寶華大廈A1428

中山辦事處地址:中山市古鎮長安燈飾配件城C棟11卡

杭州辦事處:杭州市西湖區文三西路118號杭州電子商務大廈6層B座

電話:13534146615

企業QQ:2881579535

深圳市壹芯微科技有限公司 版權所有 | 備案號:粵ICP備2020121154號